在数据洪流席卷全球的当下,数据中心作为数字时代的核心基础设施,正面临前所未有的挑战。特别是人工智能、机器学习(AI/ML)等应用的普及,对内存带宽和容量的需求急剧增长,传统内存架构的局限性逐渐显现。在这一背景下,Compute Express Link(CXL)技术因其对数据中心内存性能的跨越式提升,成为了业界关注的焦点。

Rambus半导体IP产品营销高级总监Lou Ternullo

日前,Rambus半导体IP产品营销高级总监Lou Ternullo在一次媒体采访中,深度剖析了CXL技术的特性,以及Rambus对CXL技术发展的思考。

打破内存瓶颈,重塑数据中心架构

“CXL是十年一遇的技术力量,将革新数据中心的架构。” Lou Ternullo指出,AI/ML应用导致的存储和处理需求爆炸性增长,使得传统内存系统成为关键瓶颈。传统的直接连接DRAM与固态硬盘(SSD)之间存在显著的延迟和成本差距,导致昂贵内存资源的利用率低下,内存闲置问题日益突出。

据介绍,CXL技术通过提供低延迟、高带宽的缓存一致性互连,实现了CPU与加速器之间的内存资源共享,显著提升了数据中心的灵活性和效率。Lou Ternullo进一步解释:“CXL通过低延迟内存扩展,可以满足不断增长的计算核心数量的需求。还能实现内存池化和分层,优化内存利用率。”

Lou Ternullo认为,在人工智能时代,CXL将会颠覆现有的云计算数据中心架构,以帮助企业满足日益增长的计算能力和带宽需求。

目前,该技术得到了包括超大规模云服务商、系统 OEM、平台和模块制造商、芯片制造商和 IP 提供商在内的行业巨头们的鼎力支持,其迅速发展正反映了它所能带来的巨大价值。

从参与者到引领者

“Rambus处于独特的位置,能够向CXL生态系统交付创新的解决方案。”Lou Ternullo表示,作为CXL联盟的积极参与者,Rambus在CXL技术的定义和开发过程中发挥了重要作用:“Rambus在2021年推出了针对数据中心的CXL内存计划,并紧跟技术发展趋势,相继推出了CXL 2.0和CXL 3.1控制器IP解决方案。”

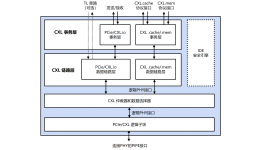

据了解,Rambus CXL 3.1控制器针对SoC、ASIC和FPGA进行了深度优化,适用于AI/ML、数据中心和边缘应用等多种场景。这些控制器不仅提供了业界领先的高带宽和低延迟性能,还集成了完整性与数据加密(IDE)和可信执行环境设备接口安全协议(TDISP)模块,确保了数据传输的安全性和完整性。

为了提升数据中心设备兼容性和系统内互连性能,Rambus基于PCIe的物理和电气接口,并通过建立一致性、简化软件堆栈以及保持与现有标准兼容性的协议来构建CXL协议。其中CXL 3.1使用PCIe 6.1的物理层,将数据传输规模扩大到64 GT/s,支持在一个x16链接上高达128 GB/s的双向通信。

Lou Ternullo透露:“为了确保CXL 3.1控制器的成功推出,我们利用了在DDR和PCIe/CXL数字IP方面的广泛专业知识,进行了大量的协同设计和优化工作。同时,我们积极听取市场反馈,将低延迟和数据完整性作为关键指标,成功开发出了具备超低延迟和端到端数据完整性的CXL 3.1控制器。”

CXL技术的新时代

在实现数据中心实现低延迟内存扩展之外,CXL还将支持内存分层和池化,优化内存利用率,降低总体拥有成本(TCO),并通过实现整个机架规模的资源解耦和可组合性,使内存、计算和I/O资源能够灵活分配和组合,满足多样化的应用场景需求。

Rambus CXL 3.1控制器通过提供低延迟、高带宽的连接,满足了各组件之间高效通信的需求,并具备多层级交换能力,为高度可扩展的内存池化和共享提供了坚实基础。这些特性将极大缓解高昂的内存成本和资源闲置问题,为下一代数据中心的发展注入强劲动力。

这种技术革新,不仅解决了当前数据中心的内存瓶颈问题,还为未来的高性能计算应用铺平了道路。Lou Ternullo表示,未来CXL技术将在数据中心中扮演越来越重要的角色。

随着数据中心解耦和可组合性的提高,安全性将成为越来越重要的考虑因素。Lou Ternullo介绍,所有三种CXL协议都通过完整性和数据加密(IDE)来保障安全,Rambus的CXL 3.1控制器集成了IDE和TDISP模块,能够在整个链路中监控并保护CXL和PCIe免受物理攻击,确保数据传输的保密性、完整性和重放保护。

“CXL预计会逐步被采用,帮助数据中心解决目前所面临的问题。” Lou Ternullo对CXL的发展充满信心。未来,随着CXL技术的不断发展和普及,Rambus将继续发挥其独特优势,开启一个全新的计算时代。